Look Ma, No CAD...

-

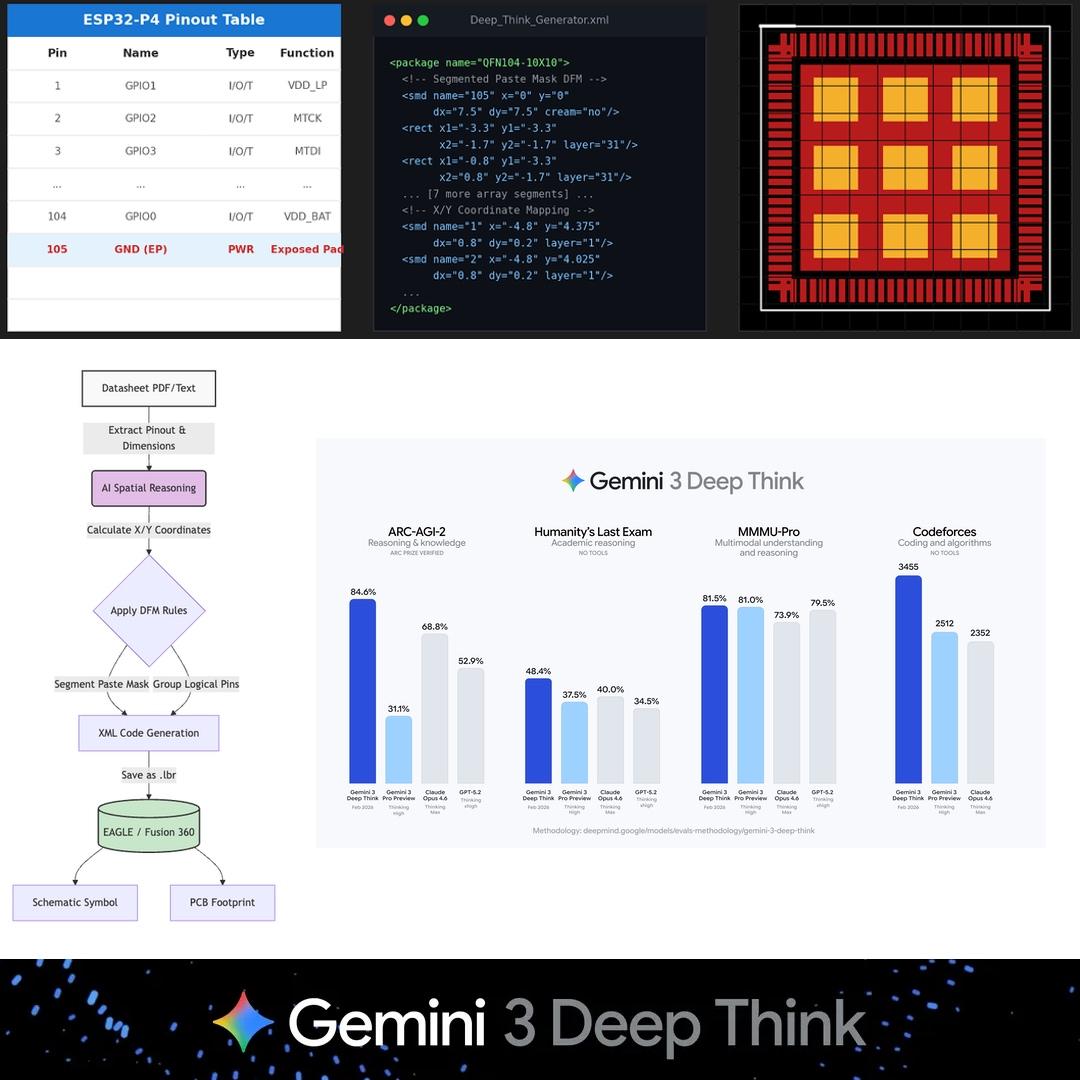

Look Ma, No CAD... We fed datasheets to Gemini Deep Think and it spit out production-ready EAGLE .lbr files... paste mask segmentation and all. ESP32-P4, MAX44009, LT3652, ES8311.

It calculated every pad coordinate, segmented the paste mask to ~40% coverage so the chip doesn't float during reflow, and grouped schematic pins by function. No footprint editor. No GUI. XML out of a chat window.

️

️

https://blog.adafruit.com/2026/02/14/from-pdf-to-lbr-using-deep-think-to-write-custom-cad-parts/

-

Look Ma, No CAD... We fed datasheets to Gemini Deep Think and it spit out production-ready EAGLE .lbr files... paste mask segmentation and all. ESP32-P4, MAX44009, LT3652, ES8311.

It calculated every pad coordinate, segmented the paste mask to ~40% coverage so the chip doesn't float during reflow, and grouped schematic pins by function. No footprint editor. No GUI. XML out of a chat window.

️

️

https://blog.adafruit.com/2026/02/14/from-pdf-to-lbr-using-deep-think-to-write-custom-cad-parts/

@adafruit

uh, i think im already seeing the culprit... -

@blue_on it's a captcha to see who reads the article -pt

-

That's pretty sweet. I'm just learning Kicad, and I didn't know about the 40% reflow rule, so thanks for that education.

For the past 25 years, I've tried to avoid proprietary closed-source tools for my software work, and now I think hardware is getting closer to having totally FOSS tool-chains, including FPGA programming and silicon chip design. I'm not exactly "looking forward" to using FOSS equivalents of what you've shown here, but I do like the idea of having reliable automated routing and layout tools in FOSS tools, like Kicad.

-

R ActivityRelay shared this topic